AI 시대 반도체 패키징 혁신: 칩렛과 유리기판의 역할

AI 발전 속 첨단 반도체 패키징이 어떻게 칩렛, 유리기판을 통해 진화하고 있는지, 그리고 PCB의 발전이 산업에 미치는 영향을 분석합니다.

도입: 왜 지금 '패키징'이 반도체 경쟁력의 중심이 되었는가

최근 몇 년간 반도체 산업의 화두는 단연 AI입니다. 거대 언어모델(LLM)과 생성형 AI의 확산으로 연산량이 기하급수적으로 늘어나면서, 단일 다이(Die) 위에서 트랜지스터 수를 늘리던 전통적인 무어의 법칙만으로는 더 이상 성능 요구를 따라잡기 어려워졌습니다. 공정 미세화의 비용은 폭증하고 있으며, EUV 공정 도입 이후 노드 전환 한 세대당 얻을 수 있는 PPA(Power, Performance, Area) 이득도 점차 축소되고 있다는 평가가 일반적입니다.

이런 한계를 돌파하기 위한 해법이 바로 첨단 패키징(Advanced Packaging)입니다. 전공정(Front-end)에서 답을 찾기보다, 후공정(Back-end)에서 여러 다이를 효율적으로 묶고 시스템 레벨 성능을 극대화하는 방향으로 산업의 무게추가 이동하고 있죠. 칩렛(Chiplet), 2.5D/3D 적층, 유리기판(Glass Substrate), 그리고 이를 떠받치는 차세대 PCB까지 — 이들은 개별 기술이 아니라 하나의 시스템 진화 흐름으로 이해해야 합니다.

이 글에서는 엔지니어 관점에서 칩렛, 유리기판, PCB의 진화가 어떻게 맞물리는지 살펴보고, 실무에서 지금 무엇을 준비해야 할지 점검해 보겠습니다.

칩렛(Chiplet)과 이종집적: 설계 패러다임의 재구성

칩렛의 정의와 오해

칩렛은 기능 블록별로 분리된 다이를 패키지 단위에서 통합하는 설계 방식입니다. 흔히 "서로 다른 공정 노드를 섞는 기술"로만 알려져 있지만, 이는 일부분에 불과합니다. 실제로는 동일 공정 노드의 다이를 여러 개로 분할하여 수율을 높이고 재사용성을 확보하는 사례도 적지 않습니다.

모놀리식 SoC 대비 칩렛 방식이 가지는 일반적 이점은 다음과 같습니다.

- 수율 개선: 다이 면적이 작아질수록 결함 확률이 낮아져 양품 수율이 향상됩니다.

- IP 재사용성: 동일한 I/O 다이, SerDes 다이 등을 여러 제품에 재활용할 수 있습니다.

- 개발 기간 단축: 검증된 다이를 조합해 신제품 개발 주기를 줄일 수 있습니다.

- 유연한 공정 매칭: 로직은 선단 노드, I/O나 아날로그는 성숙 노드를 사용하는 등 비용 최적화가 가능합니다.

이종집적을 가능케 하는 인터커넥트 동향

칩렛 시대를 본격적으로 여는 핵심은 다이 간 인터커넥트 표준화입니다. 대표적으로 UCIe(Universal Chiplet Interconnect Express)는 칩렛 간 물리·프로토콜 계층을 표준화해, 서로 다른 벤더의 다이를 한 패키지 안에서 결합할 수 있는 기반을 마련하고 있습니다.

적층 방식 또한 다양해지고 있습니다.

- 2.5D 패키징: 실리콘 인터포저나 RDL 인터포저 위에 다이를 나란히 배치하는 구조. HBM과 로직 다이를 결합하는 데 널리 사용됩니다.

- 3D 적층: 다이를 수직으로 쌓고 TSV(Through Silicon Via) 또는 하이브리드 본딩으로 연결합니다. 하이브리드 본딩은 마이크로 범프 없이 구리-구리 직접 접합을 사용해 통상적으로 더 미세한 피치를 구현할 수 있는 것으로 알려져 있습니다.

엔지니어 관점에서는 SI(Signal Integrity)와 PI(Power Integrity) 설계가 더욱 중요해집니다. 다이 간 거리가 짧아지고 데이터율이 높아질수록, 채널 손실, 크로스토크, 전원 노이즈 결합이 시스템 성능을 좌우하는 변수가 됩니다.

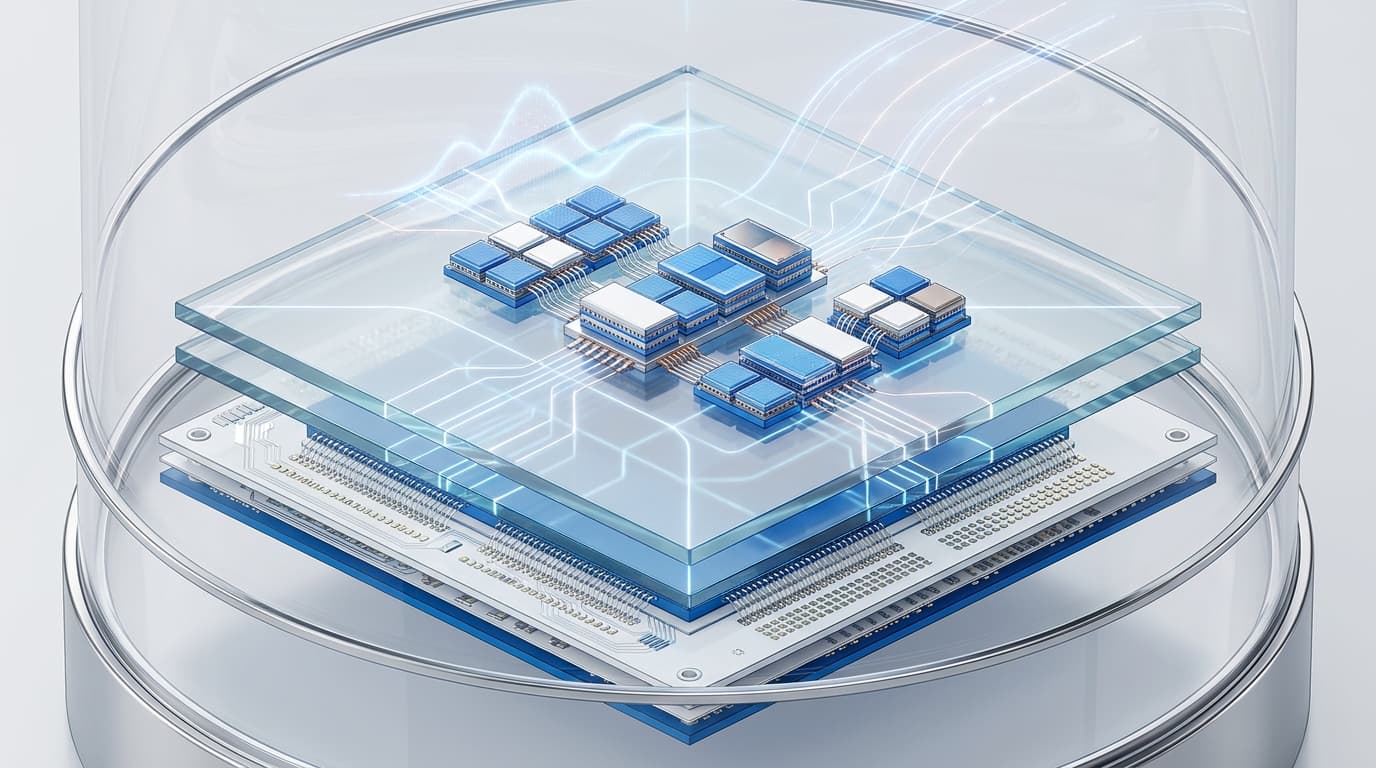

Chiplet-based 2.5D packaging architecture with interposer and HBM stacks

Chiplet-based 2.5D packaging architecture with interposer and HBM stacks

유리기판(Glass Substrate): 가능성과 현실적 과제

유리기판이 주목받는 기술적 이유

유리기판은 차세대 패키지 기판 후보로 최근 가장 활발히 거론되는 소재입니다. 기존 유기 기판 대비 일반적으로 다음과 같은 장점이 있다고 평가됩니다.

- 뛰어난 평탄도: 대면적에서도 휨(warpage)이 적어, 미세 RDL(재배선층) 구현에 유리합니다.

- 낮은 유전 손실: 고주파 영역에서 신호 손실이 작아 고속 인터커넥트에 유리합니다.

- 안정적인 CTE(열팽창계수): 실리콘 다이와의 CTE 미스매치를 줄여 신뢰성 확보에 도움이 됩니다.

- 대면적 패널 가공 가능성: 디스플레이 산업에서 축적된 패널 공정 기술을 활용할 잠재력이 있습니다.

또한 TGV(Through Glass Via)를 통해 수직 인터커넥트를 구현하면, 실리콘 인터포저를 부분적으로 대체하거나 보완하는 형태로 고밀도 패키징 구조를 만들 수 있습니다.

양산화의 벽: 비용·취성·공정 인프라

그러나 유리기판이 곧바로 유기 기판을 대체할 것이라고 단언하기는 어렵습니다. 통상적으로 다음과 같은 도전 과제가 거론됩니다.

- 취성(Brittleness): 유리는 본질적으로 깨지기 쉬운 재료이며, 핸들링 중 크랙·치핑 리스크가 존재합니다.

- TGV 가공 난이도: 레이저 또는 에칭 기반 비아 형성 공정이 기존 드릴링 대비 복잡하고, 비아 품질 검사 또한 까다롭습니다.

- 설비 투자 부담: 패널 단위 공정 전환은 잠재력은 크지만 신규 설비 투자와 라인 재구성이 필요합니다.

- 생태계 미성숙: 소재, 장비, 검사, 설계 EDA까지 전반적인 생태계가 아직 형성 단계에 있습니다.

따라서 단기적으로는 고성능 AI 가속기, 데이터센터용 패키지 등 고부가가치 영역에서 점진적 도입이 이루어질 가능성이 높다고 보는 시각이 일반적입니다.

PCB의 진화: 패키지를 떠받치는 시스템 플랫폼

SLP·HDI로의 이동과 신호 무결성

패키지가 아무리 진화해도, 결국 시스템은 PCB 위에서 동작합니다. PCIe Gen5/Gen6, CXL, 224G SerDes 같은 고속 인터페이스가 보편화되면서 PCB 설계 난이도 또한 가파르게 올라가고 있습니다.

최근 일반적으로 강화되고 있는 설계 트렌드는 다음과 같습니다.

- 미세 라인/스페이스: SLP(Substrate-Like PCB)·고차 HDI 구조를 통해 더 조밀한 배선을 구현합니다.

- 저손실 유전체 적용: 고속 신호 채널에서 Df 값이 낮은 재료 채택이 늘고 있습니다.

- 백드릴링(Back-drilling): 비아 스텁(stub)으로 인한 반사·손실을 줄이기 위해 표준적으로 적용됩니다.

- 임피던스 제어 강화: 차동 쌍의 스큐, 글래스 위브 효과까지 고려한 정밀 설계가 요구됩니다.

실무에서 점검해야 할 체크리스트로는 레이어 스택업의 대칭성, 리턴 패스 연속성, 비아 전이(transition) 최적화, 그리고 채널 시뮬레이션을 통한 마진 확보 등이 있습니다.

High-speed PCB stackup cross-section with back-drilled vias and impedance-controlled traces

High-speed PCB stackup cross-section with back-drilled vias and impedance-controlled traces

전력 무결성과 방열 설계의 중요성

AI 가속기 패키지의 전력 소비는 수백 W 수준으로 치솟았고, 일부 고성능 제품군은 그 이상으로 알려져 있습니다. 이로 인해 PDN(Power Delivery Network) 설계와 방열 설계가 PCB 단계에서 시스템 성능을 좌우하는 핵심 요소가 되었습니다.

- 저임피던스 PDN: 넓은 주파수 대역에서 타깃 임피던스를 만족시키기 위한 디커플링 전략이 필수입니다.

- BSPDN(Back-Side Power Delivery Network): 다이 후면에서 전원을 공급하는 개념이 차세대 노드에서 본격적으로 논의되고 있으며, 이는 PCB·패키지의 전원 경로 설계에도 영향을 줍니다.

- 열관리: 베이퍼 챔버, 임베디드 쿨링, 액침 냉각 등 다양한 방식이 데이터센터 수준에서 채택되고 있습니다.

PCB 단계에서부터 전력 경로와 열 경로를 함께 시뮬레이션하고, 핫스팟 분포를 사전에 예측해 카퍼 분포·비아 어레이·서멀 패드를 최적화하는 접근이 일반화되고 있습니다.

산업 경계의 붕괴: 반도체–패키지–PCB의 통합 설계 시대

Co-design이 필수가 되는 이유

예전에는 다이 설계자, 패키지 설계자, 보드 설계자가 각자의 도메인에서 일하고, 인터페이스 스펙으로만 소통하면 충분했습니다. 그러나 데이터율이 100Gbps를 넘어서고 패키지 전력이 수백 W에 이르는 지금은 다이–패키지–보드를 하나의 시스템으로 보는 Co-design이 사실상 필수가 되었습니다.

- EDA 툴 체인이 다이부터 보드까지 하나의 환경에서 시뮬레이션할 수 있도록 통합되고 있습니다.

- SI/PI/Thermal/기구 해석을 결합한 멀티피직스 시뮬레이션이 점차 표준 워크플로로 자리 잡고 있습니다.

- 조직 차원에서도 RF, 열, 기구, 전원, 신호 무결성 팀 간 협업 채널 구축이 요구됩니다.

표준화·공급망 변화가 실무에 주는 시사점

기술이 빠르게 변할수록 공개 표준의 가치는 더 커집니다. UCIe, JEDEC 산하의 메모리 규격, PCIe·CXL 등 검증된 표준을 활용해 IP와 부품의 호환성을 확보하는 전략은 향후 설계 위험을 줄이는 가장 현실적인 방법입니다.

또한 지정학적 이슈로 공급망 다변화가 가속화되는 상황에서, 엔지니어는 다음과 같은 자세를 유지하는 것이 좋습니다.

- 벤더의 마케팅 자료보다 공식 데이터시트와 검증된 측정 자료에 근거해 의사결정합니다.

- 아직 확정되지 않은 로드맵이나 차세대 스펙에 과도하게 의존하지 않습니다.

- 대체 부품·대체 공정 옵션을 사전에 BOM과 설계 단계에서 검토합니다.

결론: 엔지니어가 지금 준비해야 할 것

칩렛, 유리기판, 차세대 PCB는 각각 독립된 기술이 아니라 AI 시대의 시스템 진화라는 큰 흐름 속에서 서로 맞물려 있습니다. 패키지가 작은 보드가 되고, 보드가 거대한 패키지의 연장선이 되는 구조 속에서 엔지니어의 역량 또한 도메인 경계를 넘는 방향으로 진화해야 합니다.

단기적으로는 SLP/HDI 설계 역량과 SI·PI·Thermal 통합 분석 역량을 강화하는 것이 가장 현실적인 우선순위입니다. 중장기적으로는 칩렛 인터페이스, 첨단 기판 재료, Co-design 워크플로에 대한 학습이 경쟁력을 좌우할 것입니다.

실무 차원에서 권장하는 일반적 접근은 다음과 같습니다.

- 신기술 도입 시 공개 표준과 검증된 측정 데이터를 기반으로 점진적·실증적으로 접근합니다.

- 사내 설계 가이드와 스택업 라이브러리를 정기적으로 업데이트하고, 실패·성공 사례를 문서화합니다.

- SI/PI/Thermal 시뮬레이션을 설계 초기 단계부터 통합 워크플로에 포함시킵니다.

- 표준화 단체, 컨퍼런스, 기술 백서를 활용한 학습 채널을 조직 내에 상시 운영합니다.

패키징과 PCB의 경계가 흐려지는 지금, 가장 필요한 것은 화려한 신기술 그 자체보다 시스템 관점의 사고와 검증된 데이터에 기반한 실무 판단력일지도 모릅니다. 변화의 속도가 빠를수록, 기본기에 더 충실한 엔지니어가 결국 가장 멀리 갑니다.