혼성 신호 PCB 아트웍: 노이즈 최소화 접지 전략

혼성 신호 PCB에서 노이즈 최소화를 위한 접지 및 분리 전략을 소개합니다. 통합/분할 접지 기준과 실무 체크리스트를 통해 신호 무결성을 향상시키세요.

도입: 혼성 신호 PCB, 왜 접지 전략이 핵심인가

현대 전자 제품에서 아날로그와 디지털 회로가 한 보드에 공존하는 것은 더 이상 예외가 아니라 표준에 가깝습니다. 센서 신호를 받아 처리하는 IoT 디바이스, 고분해능 데이터 수집 장비, 오디오 코덱, 의료 계측기 등은 모두 혼성 신호(Mixed-signal) PCB의 전형적인 예입니다. 문제는 디지털 영역의 빠른 스위칭이 만들어내는 큰 di/dt가 ADC 입력이나 저잡음 증폭기(LNA)와 같은 민감 회로에 수 µV~수 mV 수준의 노이즈로 침투할 수 있다는 점입니다. 16비트 ADC 기준으로 LSB가 수십 µV에 불과하다는 점을 떠올리면, 작은 접지 임피던스 차이가 실제 분해능을 갉아먹는 주범이 될 수 있습니다.

현장에서 가장 자주 부딪히는 논쟁이 바로 "접지를 분리할 것인가, 통합할 것인가"입니다. 오래전 교과서에서는 분할 접지를 권장하기도 했지만, 최근의 IC 데이터시트와 신호 무결성(SI) 시뮬레이션 결과는 통합 접지를 기본으로 두되 상황에 따라 분할을 고려하라는 쪽으로 기울어 있습니다. 이 글에서는 노이즈 커플링 메커니즘부터 통합/분할 접지의 적용 기준, 전원 디커플링, 실무 체크리스트까지 단계별로 정리해 보겠습니다.

1. 노이즈 커플링 메커니즘 이해하기

실무에서 접지 전략을 결정하기 전에, 어떤 경로로 노이즈가 전파되는지 정확히 파악해야 합니다. 메커니즘을 모른 채 "분리하면 좋다더라"는 말만 따라가면 오히려 EMC 측정 단계에서 문제가 커지는 경우가 많습니다.

1.1 공통 임피던스 커플링과 리턴 경로

디지털 IC가 스위칭할 때 발생하는 큰 dI/dt는 공유된 접지 임피던스 Z_GND에 의해 V = L · dI/dt 형태의 전압 강하를 만듭니다. 이 전압이 그대로 아날로그 회로의 기준점에 더해지면, 입력 신호와 구분할 수 없는 노이즈가 됩니다.

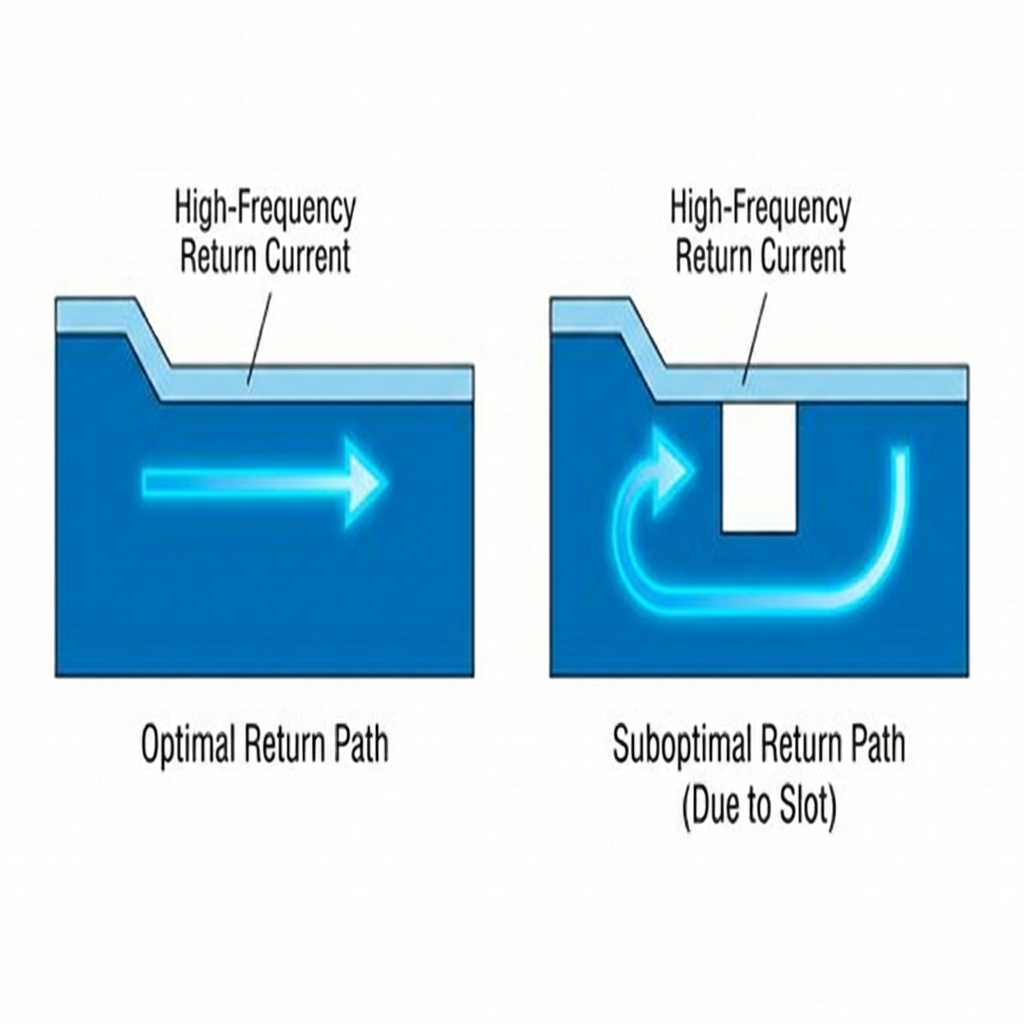

- 일반적으로 고주파 신호의 리턴 전류는 신호 트레이스 바로 아래의 접지면을 따라 흐릅니다. 이는 인덕턴스를 최소화하는 경로이기 때문입니다.

- 저주파(수 kHz 이하)에서는 저항이 가장 작은 경로를 따르지만, 통상적으로 수 MHz 이상에서는 임피던스 최소 경로(트레이스 바로 아래)가 지배적입니다.

- 따라서 트레이스만 보고 라우팅을 끝내면 안 되며, 리턴 경로가 어디로 흐를지를 항상 시각화해야 합니다.

1.2 방사 노이즈와 접지면 슬롯 효과

접지면에 슬롯이나 분할이 존재하면 리턴 전류는 그 틈을 우회해야 합니다. 이때 신호와 리턴 사이의 루프 면적이 갑자기 커지고, 해당 루프는 의도치 않은 안테나로 동작할 수 있습니다. 통상적으로 수십 MHz 이상의 디지털 클럭이나 그 하모닉에서 이러한 효과가 두드러지며, 방사 EMI 규격(예: CISPR 32) 시험에서 마진을 갉아먹는 주된 원인이 됩니다.

실무 팁: 접지면을 자르기 전에 "이 보드의 가장 빠른 신호의 리턴 경로가 어떻게 변할 것인가"를 한 번 더 자문해 보세요. 대부분의 경우 답은 "자르지 말자"입니다.

Diagram showing high-frequency return current flowing directly under a signal trace on a ground plane, with a comparison to a slotted ground plane causing detoured return path

Diagram showing high-frequency return current flowing directly under a signal trace on a ground plane, with a comparison to a slotted ground plane causing detoured return path

2. 통합 접지(Unified Ground) 접근법: 기본 원칙

대부분의 현대 혼성 신호 설계에서 출발점이 되는 전략은 통합 접지입니다. 주요 ADC/DAC 제조사들의 최신 애플리케이션 노트들도 이 방향을 권장하는 추세입니다.

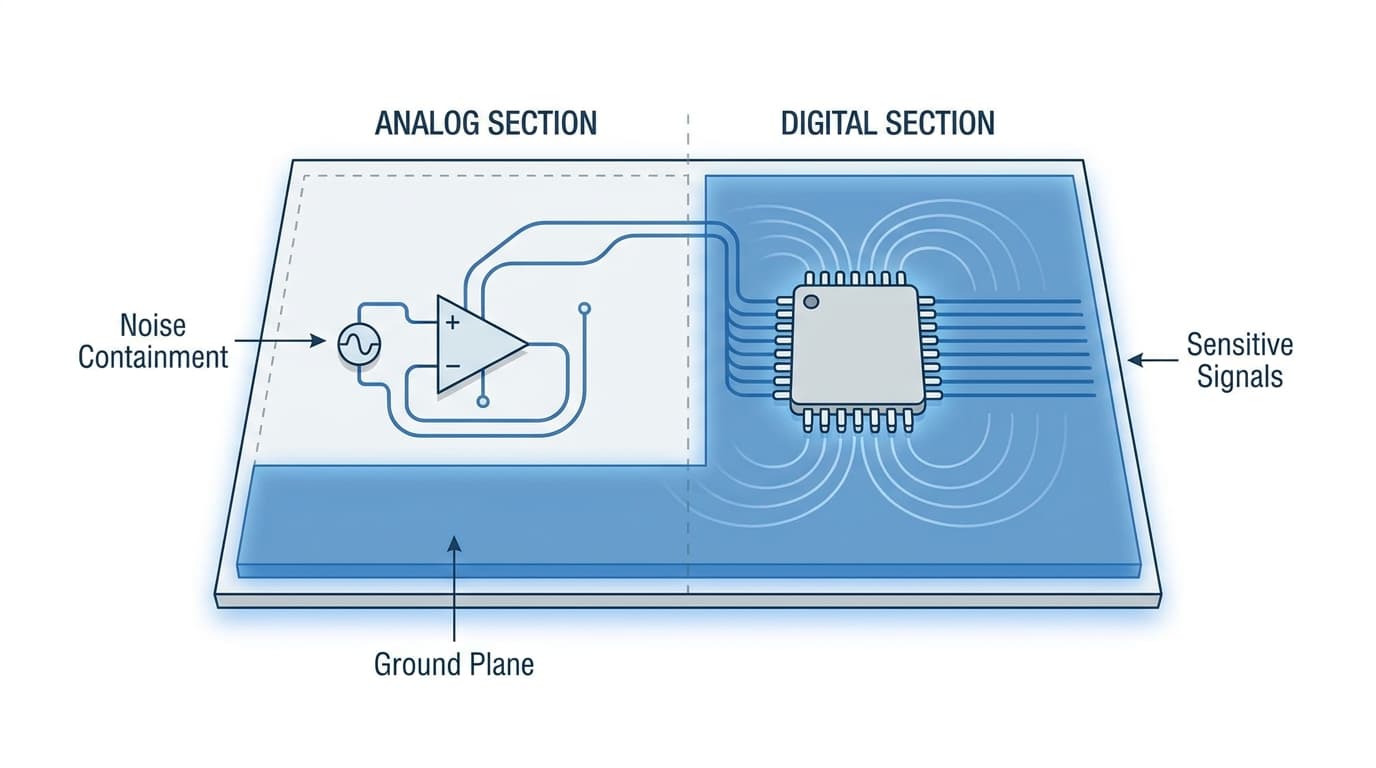

2.1 단일 접지면 + 전략적 파티셔닝

핵심 아이디어는 보드 전체에 견고한 단일 접지면을 두되, 부품 배치(파티셔닝)로 아날로그 영역과 디지털 영역을 물리적으로 분리하는 것입니다. 접지면은 끊지 않으면서, 그 위에 올라가는 부품과 신호 트레이스를 영역별로 모아주는 방식입니다.

- 아날로그 부품군(센서 프런트엔드, OP-AMP, 기준 전압원 등)은 보드의 한쪽에, 디지털 부품군(MCU, FPGA, 메모리, 클럭)은 반대쪽에 배치합니다.

- 고속 디지털 트레이스가 아날로그 영역의 접지면 위를 가로지르지 않도록 라우팅 룰(keep-out, area rule 등)을 CAD 툴에서 명시적으로 설정합니다.

- 클럭, DDR, USB와 같이 강한 노이즈원은 가능한 한 짧고 직선적인 리턴 경로를 갖도록 배치하고, 아날로그 영역과 멀리 둡니다.

2.2 혼성 신호 IC(ADC/DAC) 배치

ADC, DAC, 코덱처럼 아날로그·디지털 핀을 동시에 갖는 IC는 두 영역의 경계 위에 다리처럼 배치하는 것이 일반적인 가이드입니다. 이렇게 하면 아날로그 핀은 자연스럽게 아날로그 영역으로, 디지털 핀은 디지털 영역으로 트레이스가 빠져나가게 됩니다.

- IC 데이터시트의 권장 레이아웃을 최우선으로 참조하세요. 제조사별로 AGND/DGND 핀의 권장 처리 방법이 미묘하게 다릅니다.

- 일부 ADC는 내부적으로 AGND/DGND가 이미 연결되어 있어, 외부에서 별도로 분리하지 말 것을 명시하기도 합니다.

- 경계선을 따라 IC를 배치할 때는 디커플링 커패시터와 기준 전압 회로의 공간도 함께 확보해야 합니다.

3. 분할 접지(Split Ground)가 여전히 유효한 경우

그렇다고 무조건 통합 접지가 정답은 아닙니다. 분리된 접지가 오히려 유리하거나, 본질적으로 분리되어야만 하는 상황도 있습니다.

3.1 분할 접지가 효과적인 시나리오

- 고분해능 데이터 변환기: 16비트 이상의 ADC, 정밀 계측 회로처럼 µV 단위의 노이즈가 분해능을 직접 좌우하는 경우.

- 의료기기 절연 구간: 환자 접촉부와 시스템 접지 사이에 안전 절연이 요구되는 경우(IEC 60601 등).

- 갈바닉 절연 경계: 디지털 아이솔레이터, 트랜스포머 결합, 광 결합 등으로 본질적으로 접지가 분리되어야 하는 통신/전원 경계.

- 강한 모터/전력 스위칭 회로와의 공존: 큰 펄스 전류가 흐르는 파워 그라운드와 신호 그라운드를 분리해 공통 임피던스 커플링을 차단하는 경우.

3.2 분할 접지 설계 시 주의 사항

분할 접지를 도입하기로 했다면, 다음 원칙을 반드시 지켜야 합니다.

- 신호 트레이스가 분할 경계를 가로지르지 않도록 합니다. 가로지르는 순간 리턴 경로가 끊겨 큰 루프가 형성됩니다.

- 두 접지는 일반적으로 단일 지점(또는 변환 IC 하부)에서만 연결합니다. 여러 지점에서 연결하면 접지 루프가 형성되어 오히려 노이즈가 증가할 수 있습니다.

- 절연이 목적이라면 두 접지를 절대 직접 연결하지 말고, 필요 시 고전압용 Y 커패시터로만 결합합니다.

- 제작 전 EMC 시뮬레이션(2D/3D 필드 솔버)이나 사전 양산 보드의 실측 검증을 권장합니다.

3.3 결국 "분할 vs 통합"은 케이스 바이 케이스

회로의 신호 대역, 분해능, 절연 요구, EMC 규격, 그리고 사용하는 핵심 IC의 데이터시트 권장 사항에 따라 답은 달라집니다. 과거 양산 이력이 있다면 그때의 EMC 보고서와 실측 데이터를 참고하는 것이 가장 빠른 길입니다. "한 번 잘 됐던 방식이 다음 보드에서도 잘 된다는 보장은 없다"는 점도 함께 기억해 두는 것이 좋습니다.

Comparison illustration of unified ground plane with component partitioning versus split analog/digital ground connected at a single point under a mixed-signal ADC

Comparison illustration of unified ground plane with component partitioning versus split analog/digital ground connected at a single point under a mixed-signal ADC

4. 전원 분리 및 디커플링 전략

접지뿐 아니라 전원 라인의 노이즈 격리도 동일하게 중요합니다. 아무리 접지를 잘 깔아도 AVDD에 디지털 노이즈가 그대로 실려오면 ADC 성능은 데이터시트 스펙에 도달하지 못합니다.

4.1 AVDD/DVDD 분리 기법

- 페라이트 비드: 가장 흔한 방법. 수십~수백 MHz 대역에서 임피던스가 높아 디지털 노이즈를 효과적으로 차단합니다. 다만 비드는 임피던스 곡선, DC 저항, 정격 전류, 자기 공진 주파수를 모두 확인해야 합니다. 정격을 초과하면 포화되어 임피던스가 급감합니다.

- LC π 필터: 더 낮은 주파수까지 감쇠가 필요할 때 사용합니다. 인덕터의 SRF(self-resonant frequency)를 신호 대역과 비교해 검토합니다.

- 별도 LDO: 아날로그 전원에 전용 저잡음 LDO를 사용하는 방법. PSRR이 높은 LDO를 선택해야 효과를 봅니다. 일반적으로 정밀 계측 회로에서 가장 안정적인 결과를 줍니다.

4.2 디커플링 커패시터 배치 원칙

디커플링 커패시터는 단순히 "용량 큰 거 하나 놓으면 된다"가 아닙니다. 배치와 비아 처리가 절반 이상을 좌우합니다.

- IC의 전원 핀에 최대한 가깝게 배치합니다. 통상적으로 핀에서 수 mm 이내가 권장됩니다.

- 여러 용량을 병렬로 사용할 때는 ESL(등가 직렬 인덕턴스)이 가장 낮은, 일반적으로 물리적 크기가 가장 작은 커패시터(예:

10 nF,100 nF)를 핀에 가장 가깝게 두고, 큰 용량(1 µF,10 µF)은 그 바깥쪽에 배치하는 것이 일반적인 가이드입니다. - 커패시터 패드와 비아 사이의 거리를 최소화해 비아 인덕턴스를 줄입니다. 가능하면 양쪽 패드에서 각각 비아를 내리고, 필요 시 다중 비아를 사용합니다.

- 접지 비아는 가능한 한 가까운 접지면 층으로 짧게 연결합니다. 이는 루프 인덕턴스를 줄여 고주파 디커플링 효과를 살립니다.

5. 실무 체크리스트와 검증 방법

마지막으로, 설계 후 단계에서 자주 놓치는 점들을 체크리스트로 정리해 보겠습니다.

5.1 레이아웃 단계 체크리스트

- 접지면이 끊김 없이 연속되어 있는가? 슬롯이나 의도치 않은 분할이 있는지 시각적으로 확인.

- 고속 신호(클럭, 차동 페어, DDR 등)의 리턴 경로를 시뮬레이션 또는 시각화 도구로 점검.

- 디지털 트레이스가 아날로그 영역의 접지면 위를 침범하지 않는지 확인.

- 스택업이 적절한가? 일반적으로 4층 이상이 권장되며, 신호층은 항상 인접한 접지층과 짝을 이루도록 구성합니다.

- 혼성 신호 IC의 데이터시트 권장 레이아웃과 비교 검토.

- 디커플링 커패시터 위치, 비아 배치, 페라이트 비드 정격 재확인.

- 커넥터, 케이블 인입부의 접지 처리(EMI 필터, 차폐 처리) 점검.

5.2 검증과 측정

레이아웃 검토만으로는 한계가 있습니다. 프로토타입 단계에서 다음과 같은 실측을 병행하는 것이 좋습니다.

- 근접장 프로브 + 스펙트럼 분석기: 보드 위를 스캔해 노이즈 핫스팟을 찾습니다. 클럭 하모닉이 강하게 나오는 지점을 시각적으로 식별할 수 있습니다.

- 오실로스코프로 전원 노이즈 측정: AVDD 핀에서 직접 리플과 스파이크를 측정해 데이터시트의 PSRR 한계와 비교합니다. 측정 시 그라운드 스프링이나 짧은 그라운드 클립을 사용해 측정 루프를 최소화합니다.

- ADC 노이즈 플로어 측정: 입력을 단락한 상태에서 출력 코드의 표준편차를 확인하고, 데이터시트의 noise-free resolution과 비교합니다.

- EMC 사전 시험(Pre-compliance): 본 인증 전에 방사/전도 노이즈를 미리 측정해 마진을 확보합니다.

마치며: 실무에 적용하기 위한 일반 조언

혼성 신호 PCB 설계에서 접지 전략은 "정답"이 아니라 "선택"의 문제입니다. 다만 그 선택은 반드시 다음과 같은 근거 위에 서야 합니다.

- 기본은 통합 접지 + 부품 파티셔닝으로 시작하세요. 대부분의 응용에서 가장 안정적인 출발점입니다.

- 고분해능 변환기, 절연 경계, 강한 전력 스위칭이 있는 경우에만 분할 접지를 고려하고, 그때도 단일 지점 연결과 신호 경로 검토를 잊지 마세요.

- 핵심 IC의 데이터시트 권장 레이아웃을 항상 최우선으로 따르고, 제조사 애플리케이션 노트를 함께 검토하세요.

- 전원 디커플링과 비아 배치는 접지 전략만큼 성능을 좌우합니다. 물리적 거리와 비아 인덕턴스를 줄이는 데 시간을 투자하세요.

- 설계가 끝났다고 끝난 것이 아닙니다. 프로토타입 단계의 실측과 사전 EMC 시험을 통해 가정과 현실의 간극을 좁히세요.

결국 좋은 혼성 신호 보드는 한 번에 완성되지 않습니다. 메커니즘에 대한 이해, 데이터시트에 대한 존중, 그리고 측정을 통한 피드백이 누적될 때 비로소 안정된 설계가 만들어집니다. 다음 프로젝트에서 접지 전략을 결정해야 할 때, 이 글의 체크리스트가 한 번 더 보드를 들여다보는 계기가 되기를 바랍니다.