초고속 신호 무결성 구현: 임피던스와 차동 신호

고속 PCB 설계에서 신호 무결성(SI)은 필수입니다. 임피던스 제어와 차동 신호 아트웍 최적화로 SI 문제를 해결하세요.

도입: 왜 지금 SI가 다시 화두인가

최근 몇 년 사이 PCB 설계 현장에서 가장 자주 언급되는 키워드를 꼽으라면 단연 신호 무결성(Signal Integrity, SI)입니다. PCIe 6.0이 64GT/s의 PAM4 신호를 도입하고, DDR5는 6400Mbps 이상으로 진입했으며, 400G/800G 이더넷이 데이터센터 표준으로 자리 잡으면서, 과거에는 후공정 검증 단계에서 점검하던 SI 이슈가 이제는 스택업 결정 단계부터 다뤄야 하는 핵심 의사결정 영역으로 옮겨왔습니다.

한 자리 GHz 대역에서는 어느 정도 여유가 있던 마진이, 수십 GHz 대역에서는 비아 한 개, 안티패드 크기 0.1mm 차이만으로도 채널 성능이 흔들립니다. 본 글에서는 고속 PCB 설계 실무에서 가장 자주 부딪히는 세 가지 축, 즉 임피던스 제어, 차동 신호 아트웍 최적화, 귀환 경로(Return Path) 설계를 중심으로 현업에서 바로 적용 가능한 포인트를 정리해 보겠습니다.

1. 임피던스 제어의 기본기와 최신 트렌드

1.1 일관된 특성 임피던스 유지의 의미

고속 설계의 출발점은 결국 전송선 전 구간에서 일관된 특성 임피던스를 유지하는 것입니다. 통상적으로 적용되는 목표값은 다음과 같습니다.

- 단일 종단(single-ended):

50Ω - PCIe, SATA 등 차동 페어:

100Ωdifferential - USB 2.0/3.x 차동 페어:

90Ωdifferential

일반적으로 이 목표값을 전 구간에서 ±10% 이내로 유지하는 것을 가이드로 삼습니다. 문제는 임피던스 불연속이 발생하는 지점이 한두 곳이 아니라는 점입니다. 커넥터 천이부, 비아 구조, 패드, 본드 와이어, BGA 팬아웃 영역 등 거의 모든 천이 구간이 잠재적 불연속 지점입니다. 채널 전체를 하나의 시스템으로 보고, "어디에서 임피던스가 튀는가"를 사전에 식별하는 습관이 중요합니다.

1.2 저손실 재료와 Dk/Df의 영향

데이터율이 올라갈수록 절연재의 유전율(Dk)과 손실 탄젠트(Df)가 채널 손실에 직접적으로 작용합니다. 특히 Df는 주파수가 높아질수록 삽입 손실(Insertion Loss)을 결정짓는 핵심 변수입니다.

일반적인 FR-4 계열만 보더라도 Standard-Loss, Mid-Loss, Low-Loss, Ultra Low-Loss 등급으로 세분화되어 있고, 25Gbps급 이상에서는 Low-Loss 이상 등급이 권장되는 경우가 많습니다. 재료를 선정할 때는 다음 요소를 함께 검토하는 것이 좋습니다.

- 주파수 대역에 따른 Dk/Df 변동 곡선

- 흡습성(Moisture absorption) - 환경 변화에 따른 특성 변동

- 동박 거칠기(Copper roughness) - 표피 효과 영역에서의 추가 손실

- 층간 접착 신뢰성 및 가공성

실무 팁: 동박 거칠기는 데이터시트의 "VLP", "HVLP" 등급 표기로 구분되는데, 28Gbps 이상에서는 거칠기에 의한 손실이 유전체 손실에 버금가는 수준으로 작용할 수 있습니다.

1.3 필드 솔버와 제조 공정 변동 반영

2D 계산식 기반의 임피던스 계산은 빠르고 직관적이지만, 고속 영역에서는 한계가 분명합니다. 최근 추세는 EDA 툴에 통합된 2.5D/3D 필드 솔버를 활용해 에칭 팩터(trapezoidal cross-section), 동박 거칠기, 솔더마스크 효과, 글래스 위브(glass weave) 영향까지 반영하는 것입니다.

여기서 가장 자주 빠뜨리는 단계가 제조사 실적층 데이터의 반영입니다. 설계 단계에서 가정한 코어/프리프레그 두께와 실제 제조 시 적용되는 두께가 다르면, 시뮬레이션 결과와 실측 임피던스 사이에 5~10% 수준의 차이가 발생하기도 합니다. 보드하우스로부터 실제 스택업과 사용 재료의 데이터시트를 받아 시뮬레이션 입력값을 보정하는 절차를 표준 워크플로우에 포함시키시길 권장합니다.

PCB stackup cross-section diagram showing impedance-controlled traces with dielectric layers and copper roughness

PCB stackup cross-section diagram showing impedance-controlled traces with dielectric layers and copper roughness

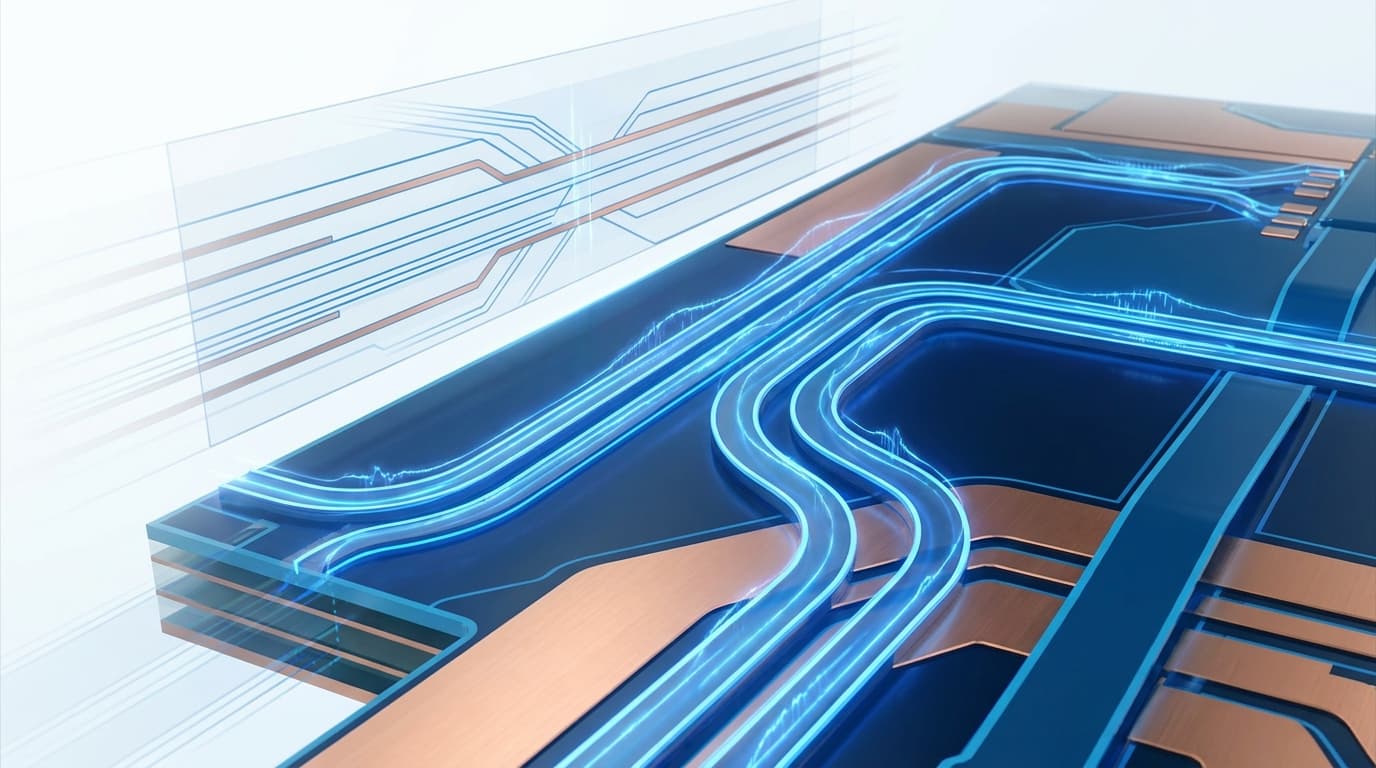

2. 차동 신호 아트웍 최적화: 길이 매칭 그 이상

2.1 Intra-pair / Inter-pair Skew 관리

차동 신호의 길이 매칭은 모든 SI 가이드의 단골 항목입니다. 일반적으로 페어 내 스큐(intra-pair skew)는 신호의 단위 시간(UI)에 대해 매우 작은 비율(통상 수 % 이하) 이내로 관리하며, 페어 간 스큐(inter-pair skew)는 인터페이스 표준에 따라 더 여유 있게 관리합니다.

여기서 자주 간과되는 점은 사행 배선(serpentine)을 어디에 두는가입니다. 스큐가 발생한 구간에서 멀리 떨어진 곳에 한꺼번에 사행을 넣으면, 그 구간 동안 두 라인의 위상 차이가 누적되면서 모드 변환(common-mode conversion)이 일어납니다. 사행은 스큐가 발생한 지점 근처에서 즉시 보상하는 것이 원칙입니다.

2.2 페어의 '동일 환경' 보장이 핵심

길이를 정확히 맞췄는데도 아이 다이어그램이 닫히는 경험을 한 번쯤 해보셨을 겁니다. 그 원인의 상당수는 두 라인의 전기적 환경이 비대칭이기 때문입니다. 차동 페어의 두 라인은 단순히 길이만이 아니라 다음을 모두 공유해야 합니다.

- 동일한 유전체 환경(같은 레이어 또는 대칭 레이어)

- 동일한 기준면(reference plane)

- 동일한 비아 구조 및 천이 패턴

- 인접 신호와의 동일한 거리·환경

예를 들어 페어 중 한 라인만 다른 레이어를 잠시 경유하거나, 한쪽만 비아 근처를 스치고 지나가면, 그 구간에서 차동 모드가 공통 모드로 변환되며 EMI와 지터의 원인이 됩니다.

실무 조언: 페어 라우팅 시 가능하면 동일 레이어·동일 길이의 평행 구간을 최대로 확보하고, 우회·분기는 페어 단위로 동시에 진행하세요. "두 라인을 한 묶음으로 본다"는 관점이 핵심입니다.

2.3 비아 구조와 백드릴링

비아는 고속 채널에서 가장 큰 임피던스 디핑(dip)을 만드는 구조 중 하나입니다. 특히 비아 스터브(via stub)는 전송선 끝단에 매달린 1/4 파장 안테나처럼 작용해 특정 주파수에서 깊은 노치를 만듭니다.

일반적으로 통용되는 가이드는 다음과 같습니다.

- 스터브 길이는 신호 최고 주파수의 1/4 파장보다 충분히 짧게 유지

- 10Gbps 이상 채널은 백드릴링(back-drilling)으로 잔여 스터브를 수십 mil 또는 그 이하로 제거

- 안티패드(anti-pad) 크기를 최적화하여 비아 구간 임피던스를 주변 전송선과 정합

- 차동 비아 쌍의 간격과 그라운드 스티칭 비아 배치를 함께 고려

안티패드를 무작정 키우면 임피던스가 과도하게 올라가고, 너무 작으면 캐패시턴스가 커져 임피던스가 떨어집니다. 시뮬레이션을 통해 채널 전체 관점에서 균형점을 찾는 것이 정공법입니다.

Differential pair routing on PCB with via transitions and back-drilled stubs visualization

Differential pair routing on PCB with via transitions and back-drilled stubs visualization

3. 귀환 경로(Return Path)와 기준면 설계

3.1 귀환 경로 연속성이 SI/EMI의 근본

고속 신호 설계에서 신호 트레이스만 그리면 절반만 한 것입니다. 신호 전류는 반드시 인접 기준면을 따라 돌아오는 경로(return path)가 필요하며, 이 경로가 끊기는 순간 임피던스 불연속, 크로스토크 증가, 복사 EMI가 동시에 발생합니다.

특히 신호가 레이어를 전환할 때, 새로 사용하는 기준면이 이전과 다른 전위라면 귀환 전류가 갈 곳을 잃습니다. 이때 자주 쓰이는 완화 기법은 다음과 같습니다.

- 레이어 전환 비아 옆에 스티칭 비아를 배치하여 동일 전위 그라운드면을 연결

- 전원면 ↔ 전원면 천이의 경우 인접 위치에 디커플링 캡(stitching cap) 배치

- 가능하면 같은 기준면을 공유하는 레이어 쌍 안에서 라우팅을 마치도록 스택업 계획

3.2 Split Plane 횡단: 원칙과 예외

"신호 라인이 분할된 기준면(split plane)을 가로지르지 않게 한다"는 것은 SI 설계의 가장 기본적인 원칙입니다. 분할면 위를 가로지르는 신호는 귀환 전류가 우회해야 하므로 임피던스가 급변하고 EMI가 폭증합니다.

다만 실무에서는 예외가 존재합니다.

- 저속 제어 신호, DC 또는 매우 낮은 주파수 신호

- 아이솔레이터를 경유해 절연이 요구되는 도메인 간 인터페이스

- 안전 규격상 의도적인 분리가 필요한 1차/2차 측 경계

이런 경우에도 무조건 횡단을 허용하기보다는 다음 완화 기법을 함께 적용하는 것이 일반적입니다.

- 횡단 지점 근처에 스티칭 캡을 배치하여 고주파 귀환 경로 형성

- 횡단 신호 수를 최소화하고 가능하면 한 지점에 모음

- 횡단이 불가피하면 단일 종단보다 차동 페어를 우선 적용 검토

- 횡단 신호의 상승 시간(rise time)을 가능한 한 느리게 유지

4. Shift-Left 접근법: 설계-시뮬레이션-검증의 유기적 통합

4.1 사전 시뮬레이션의 가치

고속 설계가 어려운 진짜 이유는 "다 그리고 나서야 문제가 보인다"는 점에 있습니다. 그래서 최근 흐름은 Shift-Left, 즉 검증 활동을 설계 초기 단계로 끌어당기는 것입니다.

Pre-layout 단계에서 다음 항목을 먼저 확정하는 것이 권장됩니다.

- 채널 손실 예산(Loss Budget) 산정: 커넥터·케이블·PCB·비아 각각의 허용 손실 분배

- 적층 구조와 재료 등급 후보 결정

- 주요 인터페이스의 토폴로지 검토(점대점 vs 멀티드롭, 종단 방식)

- 이퀄라이제이션(CTLE, DFE, FFE) 적용 여지 검토

4.2 Post-layout 검증과 측정 상관 분석

레이아웃이 완료된 후에는 추출된 S-파라미터를 기반으로 채널 시뮬레이션, 아이 다이어그램 분석, 크로스토크 평가를 수행합니다. 시제품이 나오면 TDR/VNA 측정값과 시뮬레이션 결과를 비교하여 모델의 정확도를 검증하고, 다음 프로젝트의 라이브러리에 반영하는 선순환을 만드는 것이 이상적입니다.

마무리: 실무에 적용 가능한 체크포인트

여기까지의 내용을 현장 체크리스트로 정리하면 다음과 같습니다.

- 스택업 단계: 인터페이스별 목표 임피던스, 재료 등급, 레이어별 기준면 매핑을 가장 먼저 확정

- 임피던스 관리: 필드 솔버 기반 계산, 제조사 실적층 데이터로 보정, 전 구간 ±10% 이내 유지

- 차동 페어: 길이 매칭 + 동일 환경 보장, 사행은 스큐 발생 지점 근처에서 즉시 보상

- 비아·천이부: 백드릴링 적용, 안티패드 최적화, 스티칭 비아로 귀환 경로 확보

- 기준면: 분할면 횡단 금지를 기본 원칙으로 하되, 불가피한 경우 완화 기법 병행

- 설계 프로세스: Pre-layout 손실 예산 → 라우팅 → Post-layout 시뮬레이션 → 실측 상관 분석을 표준화

고속 SI 설계는 어느 한 항목만 잘해서 되는 영역이 아닙니다. 재료, 스택업, 라우팅, 비아 구조, 귀환 경로, 시뮬레이션 워크플로우가 하나의 시스템으로 맞물려야 비로소 마진이 확보됩니다. 데이터율은 앞으로도 계속 올라갈 것이고, 그만큼 "문제를 만든 뒤 잡는 설계"에서 "문제를 만들지 않는 설계"로의 전환이 더욱 중요해질 것입니다. 오늘 소개한 원칙들을 자사 설계 가이드라인에 단계적으로 녹여 넣는다면, 다음 프로젝트의 디버깅 시간을 의미 있게 줄일 수 있을 것입니다.