PCB 설계 핵심: Via-in-Pad(VIP) 기술 완벽 가이드

VIP 기술로 HDI PCB 신뢰성 확보! 비아-인-패드의 원리, IPC-4761 표준, 비아 필링 공정, SMT 실장 체크리스트를 다룹니다.

도입부

왜 지금 VIP 기술인가?

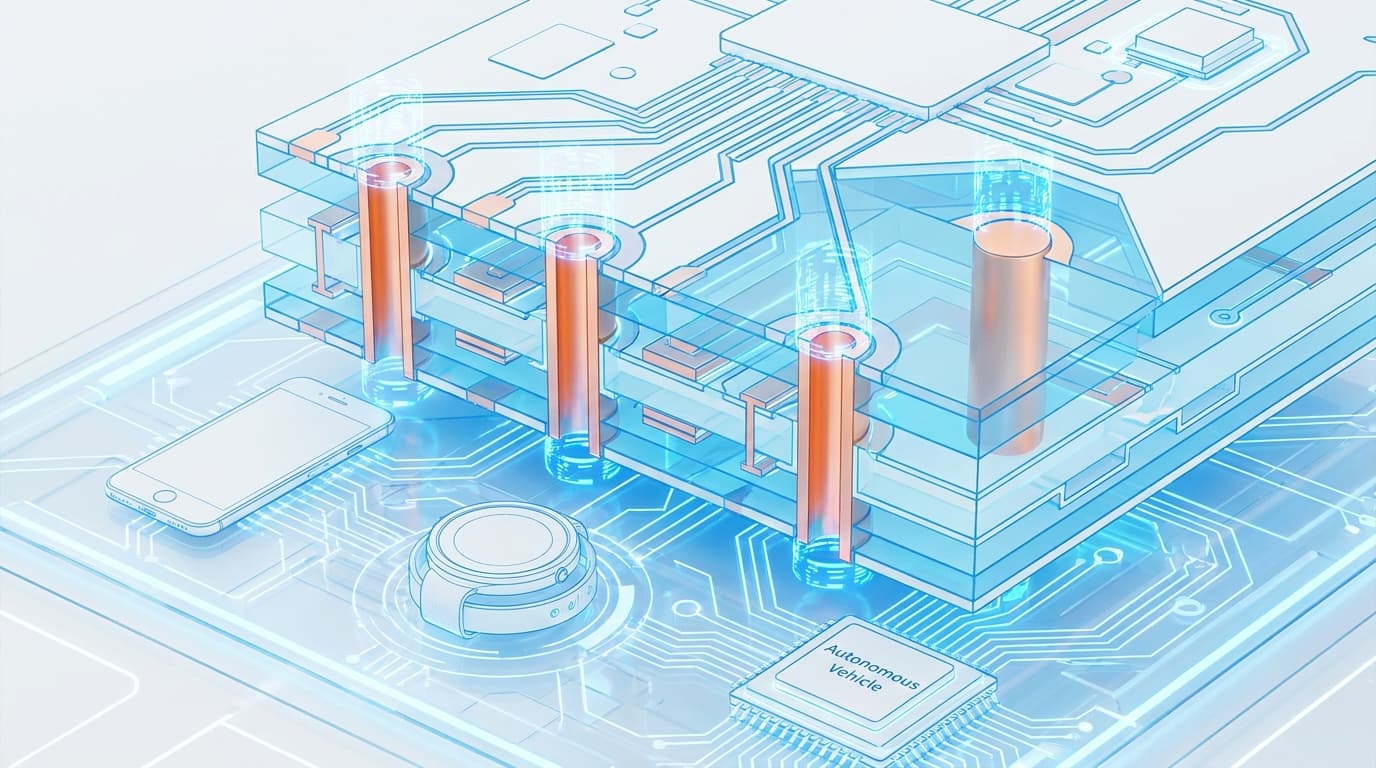

스마트폰의 두께가 7mm 아래로 내려가고, 웨어러블 기기가 손톱만 한 SoC 위에 수백 개의 핀을 집적하며, 자율주행 ECU가 한 장의 보드에 GPU·MCU·전력반도체를 모두 얹는 시대입니다. 이러한 흐름의 공통점은 단 하나, BGA·CSP의 피치가 0.4mm 이하로 좁아지고 있다는 사실입니다. 0.35mm, 심지어 0.3mm 피치까지 등장한 지금, 패드 사이로 비아를 빼내는 전통적인 도그본(Dogbone) 패턴은 더 이상 물리적으로 불가능한 영역에 진입했습니다.

이 지점에서 등장하는 해법이 바로 Via-in-Pad(VIP)입니다. 패드 한가운데에 비아를 뚫고 그 위로 부품을 실장하는 이 기술은 더 이상 첨단 제품의 옵션이 아니라, 고밀도 설계의 전제 조건이 되었습니다. 특히 국내 스타트업과 R&D 부서 엔지니어들은 "공간은 절대 부족한데 신호 무결성은 양보할 수 없다"는 모순적인 요구를 매일 마주합니다. VIP는 이 모순을 해결할 수 있는 가장 효과적인 카드입니다.

이 글에서 다룰 내용

본 가이드에서는 VIP의 기술적 원리부터 시작해 IPC-4761 표준 분류, 비아 필링 공정에서 발생하는 신뢰성 이슈, 비전도성 에폭시와 전도성 페이스트의 비교, 그리고 SMT 실장 단계까지 이어지는 실무 체크리스트를 다룹니다. 단순한 이론 설명을 넘어, 양산 현장에서 바로 적용 가능한 수치와 판단 기준을 제시하는 것을 목표로 합니다.

1. Via-in-Pad의 기술적 원리와 적용 효과

1-1. VIP가 해결하는 설계 병목

0.4mm 피치 BGA를 도그본 방식으로 라우팅하려면 패드 사이의 좁은 공간에 비아를 빼내야 하는데, 이 경우 트레이스가 통과할 수 있는 라우팅 채널이 극도로 제한됩니다. VIP를 적용하면 패드 자체가 비아 역할을 하기 때문에 패드 사이 공간이 온전히 라우팅에 할애됩니다. 실측 기준으로 동일 BGA에서 라우팅 채널을 약 30~40% 추가 확보할 수 있으며, 이는 곧 레이어 수 감소 또는 동일 레이어에서의 배선 여유로 이어집니다.

또한 패드에서 내부 레이어로 직접 수직 연결되므로 신호 경로가 짧아지고 인덕턴스가 감소합니다. DDR4/5, PCIe Gen4 이상의 고속 인터페이스에서는 비아 스텁(stub) 하나가 SI(Signal Integrity)를 좌우하는데, VIP는 스텁 길이를 최소화하여 임피던스 불연속과 반사를 줄이는 데 기여합니다.

1-2. 마이크로비아·스택 비아와의 결합

HDI 구조에서 VIP는 단독이 아니라 스택 비아(Stacked Microvia)와 결합되었을 때 진가를 발휘합니다. 1+N+1, 2+N+2 구조에서 표면 패드부터 내부 코어까지 수직으로 비아를 쌓아 올리면 Z축 집적도가 비약적으로 향상됩니다.

실제 사례로, 한 국내 스마트워치 제조사는 메인보드를 6레이어에서 4레이어로 축소하면서도 동일한 기능과 신호 품질을 구현했습니다. 핵심은 0.35mm 피치 SoC 하부에 VIP + 스택 마이크로비아를 적용해 라우팅 부담을 줄이고, BOM 비용과 보드 두께를 동시에 잡은 것입니다. 이는 단순한 공정 선택을 넘어, 제품 경쟁력을 좌우하는 설계 전략이 되었음을 보여줍니다.

1-3. 써멀 비아로서의 활용

VIP는 신호 비아뿐 아니라 열 관리 솔루션으로도 탁월합니다. QFN 패키지의 중앙 열 패드, 고출력 LED, 전력 MOSFET 하부에 VIP 어레이를 배치하면 열저항 θJA를 20~30% 개선할 수 있습니다. 비아 내부의 구리가 열을 빠르게 내부 그라운드 플레인으로 전달하기 때문입니다.

RF 회로에서도 VIP의 활용도는 높습니다. Rogers 4350B나 Arlon AD300 같은 저손실 소재로 구성된 보드에서 접지 비아를 패드 바로 아래에 배치하면 접지 인덕턴스가 최소화되어 5G mmWave, 위성통신 모듈 등에서 핵심적인 임피던스 안정성을 확보할 수 있습니다.

HDI PCB cross-section diagram showing via-in-pad structure with stacked microvias and copper-filled vias

HDI PCB cross-section diagram showing via-in-pad structure with stacked microvias and copper-filled vias

2. 비아 필링 공정과 신뢰성 이슈 심층 분석

2-1. 채움 없는 VIP에서 발생하는 다양한 신뢰성 문제

VIP의 가장 큰 함정은 "비아를 뚫었다고 끝이 아니다"라는 점입니다. 비아를 채우지 않은 상태로 SMT를 진행하면 다음과 같은 불량이 연쇄적으로 발생합니다.

- 솔더 위킹(Solder Wicking): 리플로우 과정에서 용융된 솔더가 모세관 현상으로 비아 홀에 빨려 들어갑니다. 결과적으로 패드 위 솔더량이 부족해져 BGA 볼이 들뜨거나 오픈 불량이 발생합니다.

- 보이드(Void) 형성: 비아 내부에 갇혀 있던 공기와 플럭스 잔류물이 리플로우 시 빠져나오면서 솔더 조인트 내부에 기포를 형성합니다.

IPC-A-610기준 보이드 면적이 25%를 초과하면 불합격 판정이며, BGA에서는 5% 이상부터 신뢰성 영향이 보고됩니다. - 코플래너리티(Coplanarity) 저하: 비아 입구의 함몰(dimple)로 패드 표면에 단차가 생기면,

01005부품이나 0.3mm 피치 BGA 실장에서 톰스톤·미실장 불량이 급증합니다. - 세척 잔류물 트랩과 CAF: 미충전 비아는 플럭스와 세정액을 가두는 함정이 됩니다. 시간이 지나면서 부식이 진행되거나, 습도와 전압이 동시에 작용할 때 CAF(Conductive Anodic Filament)가 발생해 절연 파괴로 이어집니다.

2-2. IPC-4761 Type VII: 업계 표준의 정착

IPC-4761은 비아 보호 방식을 Type I부터 Type VII까지 분류합니다. 이 중 Type VII "Filled and Capped"가 사실상 HDI 양산의 글로벌 표준으로 자리잡았습니다. 공정 흐름은 다음과 같습니다.

- 비아 드릴 및 1차 도금: 마이크로비아 또는 관통 비아의 내벽에 구리 도금

- 비전도성 에폭시 충전: 진공 충전 공정으로 비아 내부를 완전히 채움

- 표면 연마(Planarization): 비아 위로 돌출된 에폭시를 평탄화

- 구리 캡 도금: 평탄화된 표면 위에 추가 구리층 형성

이 4단계 공정을 거치면 비아 위 표면의 함몰(dimple) 깊이가 25µm 이내로 관리되며, 이후 OSP·ENIG·ENEPIG 등 표면 처리를 거쳐 SMT 단계로 넘어갑니다. 이렇게 확보된 표면 평탄도는 0.3mm 피치 BGA의 안정적인 실장을 보장합니다.

3. 비전도성 에폭시 vs 전도성 페이스트: 무엇을 언제 선택할 것인가

3-1. 비전도성 에폭시 필링의 강점

현재 양산 제품의 90% 이상이 비전도성 에폭시 필링을 채택하고 있습니다. 그 이유는 명확합니다.

- CTE 매칭: 전용 수지의 열팽창계수는 일반 FR-4(약

14~17 ppm/°C)와 유사하게 설계됩니다. 덕분에-40°C ~ +125°C열사이클을 1,000회 이상 반복해도 비아 크랙 발생률이 현저히 낮습니다. - 표면 평탄도: 캡 도금 후 ±25㎛ 이내 확보가 가능해 0.3mm 피치 BGA, 01005 칩 부품 실장에 적합합니다.

- 전기적 절연: 비아 내부가 절연체이므로 임피던스 불연속이 최소화되며, 고속 디지털·RF 회로에서 유리합니다.

단점으로는 비아 자체는 전기적으로 비활성이라 추가 캡 도금이 필수이며, 리드타임이 1~2일 증가하고 단가가 약 10~20% 상승한다는 점이 있습니다.

3-2. 전도성 페이스트 필링의 활용처와 한계

전도성 페이스트(은·구리 충전 에폭시)는 특정 용도에서 여전히 유효합니다.

- 장점: 비아의 전류 통전 능력을 보강하고, 별도 캡 도금 없이도 일부 표면 처리 적용이 가능하며, 써멀 비아에서 약간의 열전도 우위를 가집니다.

- 한계: 페이스트의 CTE는

30~50 ppm/°C수준으로, 구리(17 ppm/°C) 대비 격차가 큽니다. 장기 열사이클에서 비아 크랙, 도금 분리 등 신뢰성 문제가 보고됩니다.

따라서 적용 권장처는 단기 수명 소비자 제품, 비용 민감 양산품, 일부 전원 비아 등 특수 목적에 한정됩니다.

3-3. 선택 가이드라인

- 제품 수명 5년 이상, 자동차·의료·산업용 → 비전도성 에폭시 + 캡 도금 필수

- 소비자 가전, 단기 라이프사이클 제품 → 전도성 페이스트 검토 가능

- RF·고속 디지털(5Gbps 이상) → 비전도성 에폭시 강력 권장

- 고전류 전원 비아 → 전도성 페이스트 또는 구리 페이스트 고려

Comparison illustration of non-conductive epoxy filled via versus conductive paste filled via with copper cap plating

Comparison illustration of non-conductive epoxy filled via versus conductive paste filled via with copper cap plating

4. VIP 적용 시 SMT 공정에서 반드시 챙겨야 할 포인트

4-1. 스텐실 어퍼처 최적화

VIP 패드는 일반 패드와 동일한 어퍼처를 사용하면 솔더가 과도하게 도포되어 BGA 볼 사이 브릿지나 솔더 볼 튀어 오름이 발생할 수 있습니다. 일반적으로 VIP 패드의 솔더 페이스트 양은 일반 패드 대비 70~85% 수준으로 축소하는 것이 권장됩니다.

- QFN 열 패드: 50~70% 면적 비율로 분할 어퍼처 적용 (보이드 저감)

- BGA VIP 패드: 일반 패드 대비 80% 면적, 모서리 라운드 처리

- 스텐실 두께: 0.3mm 피치 이하에서는

100~120㎛스테인리스 스텐실, 전기 연마 마감 권장

4-2. 리플로우 프로파일 관리

VIP 보드는 비아 내부에 갇힐 수 있는 미세 가스 배출을 위해 예열 구간을 충분히 확보해야 합니다. 일반적으로 150~180°C 구간에서 60~90초 유지하여 플럭스 활성화와 휘발성분 배출을 유도합니다. 또한 피크 온도 도달 후 액상 상태(TAL, Time Above Liquidus)는 45~70초로 관리해 보이드를 줄입니다.

4-3. 입고 검사와 신뢰성 평가

VIP 보드를 EMS에 의뢰할 때는 다음 항목을 반드시 사양서에 명시해야 합니다.

- 비아 필링 방식(IPC-4761 Type 명시)

- 캡 도금 두께(

15㎛ 이상권장) - 비아 표면 함몰(Dimple) 깊이 (25µm 이내)

- 열사이클 신뢰성 시험 조건(

-40°C/+125°C, 1,000 cycles) - 크로스 섹션 분석 보고서 제공 여부

마무리: 신뢰성 있는 VIP 구현, 파트너십이 좌우합니다

Via-in-Pad는 단순히 "패드에 구멍을 뚫는 기술"이 아닙니다. 설계 단계의 스택업 결정부터 비아 필링 공정의 화학·기계적 관리, 그리고 SMT 단계의 스텐실·리플로우 최적화까지, 전 공정의 통합적 품질 관리가 요구되는 시스템 기술입니다. 어느 한 단계라도 어긋나면 보이드, 크랙, 코플래너리티 불량으로 직결됩니다.

floworx는 1~20레이어 HDI PCB 제작과 01005 부품·미세 피치 BGA 실장을 아우르는 EMS 역량을 바탕으로, VIP 적용 프로젝트에서 설계 검토(DFM)부터 비아 필링, 스텐실 제작, SMT 양산, 그리고 BOM·재고 관리까지 원스톱으로 지원합니다. Rogers·Arlon 기반 RF 보드, 자동차·의료용 고신뢰성 보드, 스타트업의 시제품 빠른 양산 전환까지 다양한 영역에서 검증된 프로세스를 제공합니다.

HDI 시대의 신뢰성은 결국 설계와 제조가 얼마나 긴밀하게 협업하는가에 달려 있습니다. VIP 적용을 고민하고 있다면, 초기 설계 단계부터 EMS 파트너와 함께 검토를 시작하시기 바랍니다. 그것이 양산 수율을 가르는 가장 확실한 방법입니다.